文|半导体产业纵横

2022年1月15日,PCI-SIG组织宣布PCIe 6.0规范标准v1.0版本正式发布。

PCIe 6.0被称作是21世纪以来PCIe最大的历史变化,PCIe 6.0规范将PCIe 5.0规范(32GT/s)的带宽和功率效率提高了一倍,同时可提供更低的延迟。

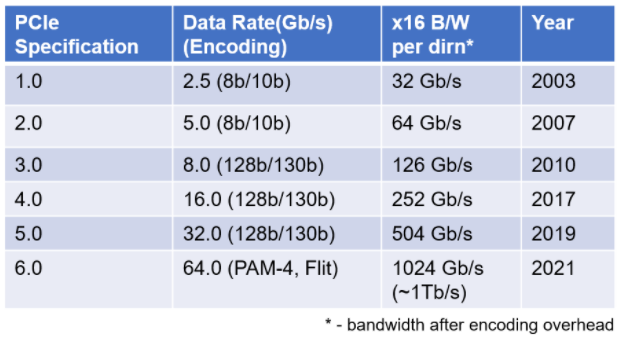

此前PCIe 5.0/4.0/3.0都采用基于NRZ(Non-Return-to-Zero)的128b/130b编码。PCIe 6.0则改用PAM4脉冲调幅信令,1b/1b编码,单个信号就能有四种编码(00/01/10/11)状态,比之前翻番,允许承载最高30GHz频率。PCIe6.0具有4级 (PAM4) 信号的脉冲幅度调制,可以实现轻量级前向纠错 (FEC) 和循环冗余校验 (CRC),减轻与PAM4信令相关的误码率,并保持了前几代PCIe技术相同的向后兼容性。

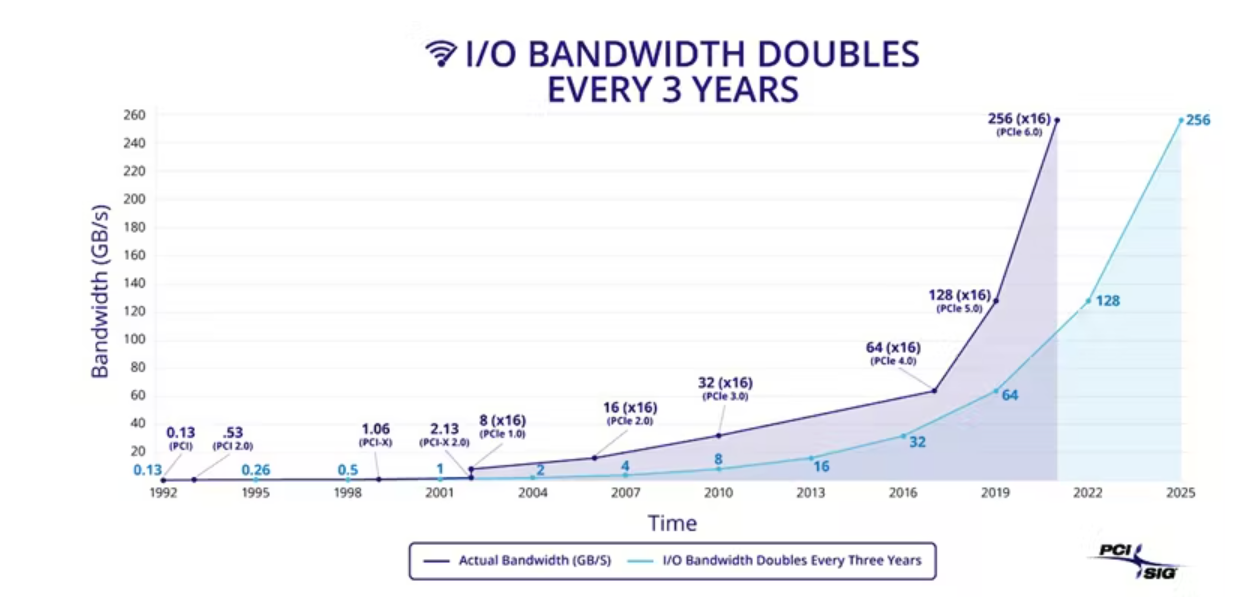

PCI-SIG的路线图曾表示,I/O带宽每三年会翻倍。但是,PCIe的技术快速迭代并没有带来PCIe的市场需求,目前市场进步已经远远滞后于技术。

PCIe6.0不起波澜

虽然这是一个争抢科技首发的时代,但是在PCIe 6.0的使用上,头部公司却又讳莫如深。如上文所说,英特尔、AMD都刚刚开始发布5.0的面世计划,英伟达也只是表态推出BlueField-3 DPU支持PCIe 5.0。

在6.0发布之前、发布之后,除IP、设计公司之外,仍鲜有产品公司表态。

最快推出PCIe 6.0产品的公司是Rambus,它今年在全球首个发布了完全符合PCIe 6.0的控制器,但是没有展示实物。

Rambus的PCIe 6.0接口控制器支持64GT/s传输数据率,x1通道满足8GB/s的单向物理带宽(相当于PCIe 4.0 x4),x16达256GB/s,双向512GB/s。新一代PAM4脉冲调制同样在线,编码状态翻番到4个,最高可承载30GHz频率,而且加入FEC(前向纠错)用来纠正信号错误。

但最新推出的Rambus产品并不是民用,它主要针对数据中心、人工智能、机器学习、HPC、汽车、物联网、和航空航天等领域。除了Rambus,群联也表示已经开始为PCIe 6.0 SSD开发低级组件,并预计将在2025年至2026年推出。

IP和设计在PCIe 6.0上的动作更早,PCI SIG发布PCIe 6.0规范最终草案几周后,Cadence推出首批经过硅验证的IP封装之一,使芯片开发人员能够在他们的设计中实施PCIe 6.0支持并对其进行测试,将使早期采用者能够在2022年至2023年为芯片添加对PCIe6.0的支持。

Cadence的PCIe 6.0 IP包括一个控制器和一个基于DSP的 PHY(物理接口)。该控制器采用多数据包处理架构,在x16配置中支持高达1024位宽的数据路径,并支持PCIe 6.0的所有关键特性,例如高达64 GT/s的数据传输速率(双向)、具有四级 (PAM4)信令的脉冲幅度调制、低延迟前向纠错 (FEC)、FLIT 模式和 L0p电源状态。

比Cadence更早,新思去年3月就宣布了针对 PCI Express (PCIe) 6.0 技术的完整 IP 解决方案,其中包括控制器、PHY 和验证 IP,支持 PCIe 6.0 片上系统 (SoC) 设计的早期开发。

青黄不接的三代接口

实际上,目前大多公司新发布的都是关于PCIe 5.0协议的接口。

2021年10月,英特尔发布的基于Alder Lake的处理器12代酷睿,使用PCIe5.0标准,其面向数据中心的下一代处理器SapphireRapids也增加PCIe 5.0。而AMD方面,在2022年开年发布会上,苏姿丰博士表示AMD在2022年下半年即将发布的Zen4架构和AM5平台也将支持PCIe5.0。AMD与Intel的入局,也标志着PCIe 5.0的大规模商用已经全面开花。

在存储SSD方面PCIe 5.0也在落地生根。去年7月,三星电子预告了其首款PCIe 5.0 SSD,将面向数据中心支持PCIe 5.0 x4(单端口)或者PCIe5.0 2x2(双端口),总带宽16GB/s。三星的这款SSD预计将于2022年第二季度推出。

除三星之外, Marvell也在去年5月底发布其首款PCIe 5.0 NVMe SSD控制器Bravera SC5系列。铠侠在去年9月表示即将推出支持PCIe 5.0及EDSEF E3.S接口的企业级SSD CD7系列,目标在2021年年底推出市场。国产公司澜起科技2021年上半年表示PCIe 5.0高速接口物理层关键IP研发取得重要进展,为PCIe 5.0 Retimer芯片的研发做好了支持。

除了原厂外,IP和设计公司也在PCIe 5.0上出力颇多,2021年2月新思交付业界首个符合PCIe5.0和CXL2.0规范的完整性和数据加密安全IP核模块;5月,Cadence宣布面向台积电N5支持PCIe 5.0规范的IP产品,该IP将于今年下半年可应用于TSMC N3工艺技术,而基于TSMC N3工艺技术的下一个版本将于2022年初流片。

PCIe 5.0标准在2019年5月便已定稿,距离其上一代PCIe 4.0的发布时间2017年正好两年,按照3年一次迭代的周期来看,这次迭代时间极短。同时,PCI 3.0到4.0的发展的时间又极长,因此,硬件厂商和客户可能面对PCIe 3.0、PCIe 4.0和PCIe 5.0三种接口共生的局面。

从上图可以看出,PCIe从4.0开始比之前的世代更新时间更短,速度更快。但即使到今天,2017年就已经出现的PCL 4.0还没有普及。

到刚刚过去的1月,英特尔支持PCIe 4.0的Alder Lake产品出货不如预期,市场回应到PC OEM为求出货回头加单PCIe 3.0 SSD,但供应端在物料准备上已逐步转向PCIe 4.0,而出现供需落差。存储方面同样不尽人意,在去年,PCIe 4.0的硬盘份额只有10%,业内预测PCIe 4.0硬盘要想成为主流需要到2023年。

PCIe 3.0是目前的最主流的接口,PCIe 4.0成本仍然具有很大风险性。

多世代并行竞争仍会持续

当前PCIe 4.0仍未充分普及,PCIe 5.0便已进入市场,接着又诞生了PCIe 6.0,这也让PCIe的升级路线出现分歧。整体而言,PCIe 6.0规格才刚问世,预期最快两年后才会有实际产品,产品市场仍需观察,目前主要问题出在PCIe 4.0与5.0之间。

固然目前PCIe 4.0的产品应用要比5.0成熟许多,但到了2022年下半与2023年初以后,PCIe 5.0的产品选择将比现在丰富许多,成本也将下降,届时对于既有的PCIe 3.0用户来说,便有升级到PCIe 4.0或直接跳到5.0的两种选择。

短期来看,可能会形成PCIe 4.0与5.0高低规混合应用的形势,通用型主机与周边装置使用成本较低的PCIe 4.0,高效能型主机与周边则用PCIe 5.0。但长期来看,若PCIe 5.0组件与周边的成本下降得够快,那么直接跳到5.0世代或许更具吸引力。PCIe 5.0平台可视情况使用5.0、4.0或3.0的周边装置,但PCIe 4.0平台则无法发挥5.0设备的效能,因而直接升级使用5.0平台,将是更具灵活性的选择。

评论