文|美股研究社

去年,我一直在详细介绍台积电(纽约证券交易所代码:TSM)的绝唱(最初的迹象可以追溯到更远),因为台积电在遵循摩尔定律方面的进展似乎与英特尔(纳斯达克股票代码:INTC )类似) 回到 10nm。

在我看来,随着最新信息的披露,台积电在 10nm 工艺上将经历与英特尔类似的五年“黑暗时代”,现在有很多危险信号,台积电的制程领导地位现在已经完全站不住脚。

这在不久前是完全不可想象的,证明台积电的技术地位正在迅速恶化。投资者应该意识到,台积电很快将不再是他们可能仍然认为自己正在投资的行业领导者。到那时,只有惯性——以及竞争对手快速建立新晶圆厂的能力——才能让台积电继续前进。尽管如此,我预计客户很快就会对台积电缺乏进展感到不满,这使英特尔成为无可争议的受益者。

台积电的低预期

摩尔定律指出,芯片上的晶体管数量应每两年翻一番,半个多世纪以来,它一直是衡量半导体进步的金蜡烛。由于芯片尺寸大致保持不变,这实际上意味着晶体管密度(即针对相同面积归一化的晶体管数量)应该每两年翻一番。

在这方面已经普及的度量标准是 MTr/mm2(每平方毫米数百万个晶体管),为方便起见,将进一步缩写为简单的 MT。比如Intel的10nm(改名为Intel 7)的密度是100MTr/mm2,或者干脆是100MT。

1、N5差于预期

虽然 N5 作为台积电在 2018 年从英特尔手中夺取制程领先地位的 N7 的继任者,在 2020 年推出的苹果( AAPL )A14中延续了台积电的领导地位,但迄今为止,台积电对实际工艺规格仍然非常模糊,此外说 N5 与 N7 相比缩小了 1.8 倍(略低于 2 倍基准,但符合台积电每个节点的平均缩小)。这让很多人得出结论,N5 的逻辑密度达到了 171MT 甚至更高,远超 Intel 最先进的 10nm/7 工艺的 100MT。

然而,Angstronomics基于实际测量的新分析表明,情况并非如此。虽然在 2020 年苹果公司报告 A14 的晶体管数量时,N5 没有实现预期缩小的第一个暗示已经浮出水面,但实际的晶体管测量提供了确凿的证据,即 N5 实际上只实现了 1.52 倍的缩小。

对于投资者来说,这应该是一个危险信号。

2、N3也比预期差

正如投资者所知,积累财富的关键是复合回报。然而,反过来也是正确的:以较低的复合年增长率进行复利将显着降低累积长期回报。

因此,鉴于 N5 带来的收缩低于预期,这会流向 N3,因此也提供低于预期的密度。例如,几年前曾预计 N3 将提供约 300 公吨的密度。然而,上述信息得出的新(初步)密度估计仅为 215 公吨。

虽然较低的密度肯定会降低节点的绝对竞争力,但最终重要的是相对竞争力,例如英特尔此后也推迟了其 7nm 节点(更名为英特尔 4)。

在这方面,最近英特尔在一次会议上透露了相当多的信息。最令人惊讶的是,英特尔 4 基本上已沦为一个权宜之计节点,只有一个高性能逻辑库。作为比较,以前的节点具有三个库以及更多功能,例如 I/O 和模拟。

因此,尽管 Intel 4 提供了 2 倍的扩展(因为 CPU 大量使用高性能库),但节点的理论最大密度(本文的主题)仅为 123MT。因此,直到 2024 年初的 Intel 3,Intel 才会再次实现密度的重大飞跃。根据我的分析,2-1 库(数字代表每个 PMOS 和 NMOS 晶体管的鳍片数量)应该提供大约 200MT 的密度,而 1-1 库可以提供超过 230MT 的密度,超过 TSMC 的 N3。虽然 TMSC 正在开发更高密度的 N3S 节点,但它的精确时间尚不清楚。

为了完整起见,请注意,目前这只是猜测,因为英特尔甚至还没有正式确认英特尔 3 将有一个高清库,只是说它将有一个“更高密度的惠普库”。尽管如此,英特尔的每个 FinFET 节点(从 22nm 开始)都有一个高清库,如果英特尔 3 没有一个高清库,这将是令人惊讶的,特别是因为英特尔 3 也是针对英特尔代工服务客户的。

另外,我对2-1或1-1 fin库的猜测是在台积电宣布自己的N3 2-1库之前做出的,而N3S很可能是1-1库;这验证了 2-1 库是合理的。总之,2-1 库将使英特尔在鳍片数量和整体晶体管密度方面基本上与台积电相当(英特尔 3 大约为 200 吨,而 N3 大约为 215 吨)。尽管英特尔在上市时间方面会晚一年。

我在 2020 年的初步分析表明,英特尔 4(当时称为 7nm)在晶体管密度方面将落在 N5 和 N3 之间。但是,根据目前的信息,仅考虑 HP(高性能)库时,Intel 4 实际上似乎比 N5 更接近 N3,而由于缺少 HD(高密度)库,Intel 4 在最大密度方面明显落后。因此,直到英特尔 3,即英特尔 4(和 N3)一年后,英特尔才会推出新的高清库。不过,与 HP 库的情况类似,Intel 3 HD 库实际上应该与 N3 差不多。

3、N2 也比预期的差

英特尔 3 不仅比之前预期的更接近台积电 N3,而且 N2 也一直在违背预期的下行空间。如前所述,N2 的时间安排使该节点比 N3 的节奏慢了 3 年,而 N3 本身已经处于相对缓慢的 2.5 年节奏,同时也带来了约 1.55 倍的平庸收缩。

但血腥屠杀仍在继续。台积电最近在其技术研讨会上提供了更多关于 N2 的信息,而且非常糟糕。台积电表示,预计 N2 将带来“1.1 倍”的缩小。这个数字是基于 50% 逻辑、30% SRAM 和 20% 模拟的芯片组成。即使假设 SRAM 和模拟根本不缩小,那么逻辑缩放比例应该在 20-30% 左右(除非 TSMC 出于某种原因显着降低了 >1.1 倍的数字)。

最终,这意味着在 2026 年 N2 投放市场时,台积电将提供人们直到最近才真正期待 2023 年 N3 的晶体管密度。

扩展趋势与英特尔

如果以上听起来台积电不会有竞争力而失去领导地位,这似乎是正确的。虽然如上所述还没有官方确认,但 Bob Swan 在 2019 年底曾表示 7nm(英特尔 4/3)和 5nm(20A/18A)都将实现 2 倍的缩小。

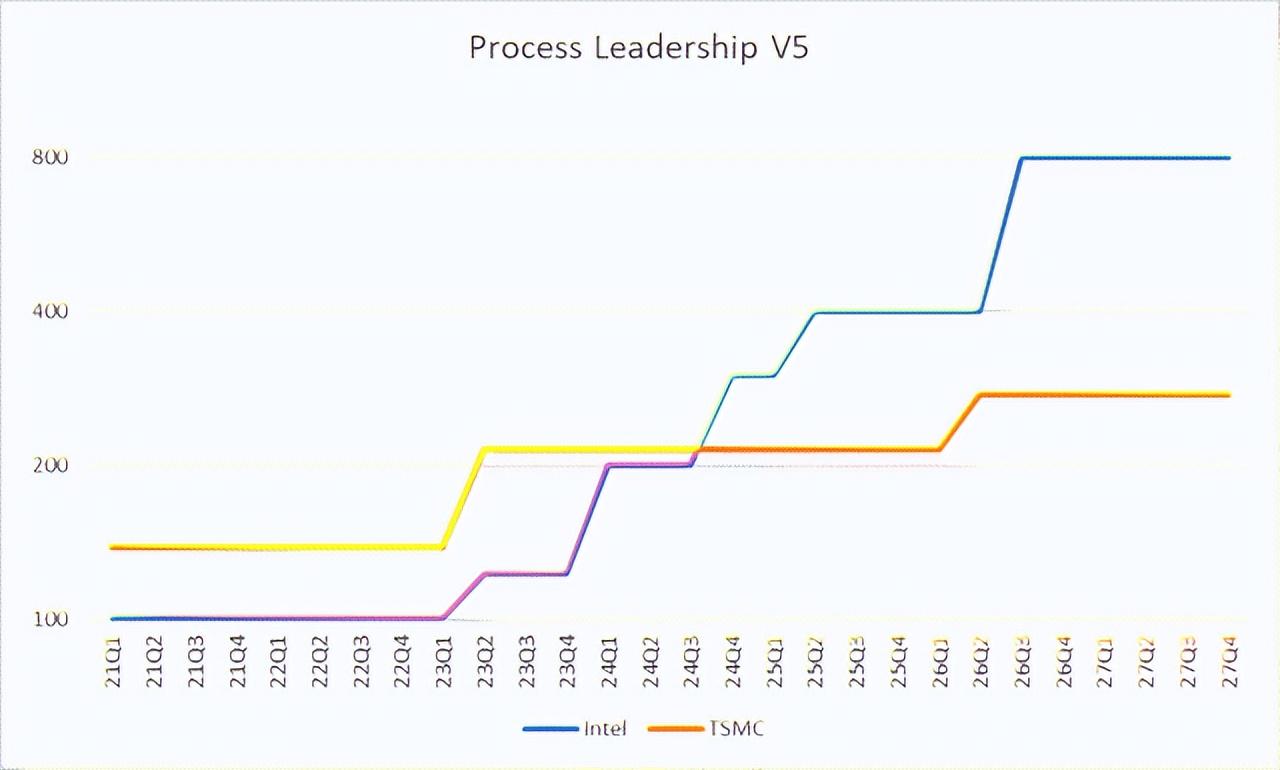

从那以后,英特尔进一步表示,它可以在超过 20A/18A 的节点上实现 40-100% 的密度进一步增加。从表面上看,这意味着到 2025 年初,英特尔可能会提供 400 吨的晶体管密度,到 2026 年将达到 800 吨。从上面的讨论中,N2 几乎完全没有规模化意味着台积电在 2026 年甚至可能很难达到 300 吨。

这意味着,在最坏的情况下,到 2026 年,英特尔的晶体管密度可能是台积电的 3 倍。这将是一个令人震惊且非常迅速的消亡。

总体而言,从 N5 到 N3 再到 N2(时间是从 Q3'20 到 Q2'26),台积电将在 6 年内实现约 2 倍的扩展,复合年增长率为 13%。相比之下,从英特尔 4 到 3 到 20A 到 18A 到 14A(时间是从 23 年第二季度到 26 年第四季度),英特尔将在 3.5 年内实现约 6.5 倍的扩展。

需要明确的是,对于台积电来说,直到 N3 的数字基本得到确认,而根据台积电本身的说法,所讨论的 N2 仅代表轻微的收缩(>1.1x”)。对于英特尔来说,直到英特尔 4 的数字得到确认,而英特尔 3 假定英特尔 7 缩小了 2 倍,英特尔 18A 假定英特尔 3 缩小了 2 倍。此信息来自 Bob Swan 在 2019 年谈到“7nm”和“5nm”时“缩小。显然,其中一些目标可能在过去三年中发生了变化。

最后,2026 年的 14A 节点假设再缩小 2 倍。这个节点也有一些假设,尽管总体假设是英特尔将简单地以继续遵循摩尔定律为目标。例如,2021 年 10 月 Pat Gelsinger 表示,结合英特尔的 3D 封装,他预计未来十年英特尔的发展速度将超过摩尔定律。特别是,假设该节点引入了英特尔在 2021 年 12 月披露的“CFET”晶体管架构,并评论说这可以实现 30-50% 的缩小。虽然此处假设的 50% 缩小(2 倍密度)处于该范围的高端,但即使 14A 实现了 0% 的缩小,英特尔仍将保持其领先地位。

英特尔为自己设定的目标是继续摩尔定律,每个节点(每两年)将晶体管密度提高 2 倍。为了重新夺回制程领先地位,英特尔正在通过将节奏加速至 20A(这两个节点之间仅相差 18 个月左右)来弥补英特尔 4 的延迟。

另一方面,台积电在 N5(~1.5 倍)开始显着减缓其密度扩展并在 N2(估计为~1.25 倍)接近停滞,同时在 N3 和 3 也显着放缓至 2.5年才能达到 N2。

风险及注意事项

正如英特尔披露的英特尔 4 所表明的那样,主要困难在于工艺技术和实际芯片通常由几个不同的“单元库”组成,每个单元库在性能、功率和面积 (PPA) 方面都有不同的权衡。

首先,这意味着本文的讨论有点学术性。例如,英特尔(在大多数情况下)一开始甚至没有为其 CPU 使用 100MT HD 库,因为 CPU 旨在达到尽可能高的时钟速度(性能)。尽管如此,正如上面引用的 Angstronomics 文章所示,理论和实际实现的晶体管密度之间仍然存在很强的相关性。举个假设的例子,如果 Intel 3 和 TSMC N3 的密度都在 210MT 左右,那么在这两种工艺上制造的 Apple SoC 应该会产生大致相同的芯片尺寸。

其次,更重要的是,不同的库可能会在节点之间实现不同的收缩。在这种情况下,虽然英特尔已经详细说明了英特尔 4 HP 库是如何实现 2 倍缩小的,但还不能肯定地说这将如何转化为英特尔 3 的高清库。事实上,英特尔 4 节点并没有甚至一开始就有一个高清库。这种实践上的变化也为 20A 和 18A 引入了一些问号。虽然,由于 18A 的引入,与英特尔 3 的一整年相比,该节点将比 20A 落后大约半年(与英特尔 4 相比)。

因此,英特尔在 2024 年和 2026 年可能达到 400MT 和 800MT 的密度的推断并不确定,因此可能需要修改(如果当年没有高清库可用)。尽管如此,由于台积电提供的信息暗示它将在 2023 年达到 215 吨,在 2026 年达到 270 吨左右,因此英特尔重新获得晶体管密度领先地位的安全边际似乎非常大,即使英特尔的密度低于目前的预期。

最后一个风险是更多的心理风险。回到 14nm 左右,英特尔不断对其晶体管密度的领先地位大肆宣传。相比之下,目前英特尔管理层仍然对重新获得晶体管密度领先地位一无所获。英特尔唯一声称的是,到 2025 年它将重新获得每瓦工艺性能的领先地位。人们会假设英特尔管理层会在屋顶上尖叫(就像它最初在 14/10nm 所做的那样),如果它真的能获得材料优势超过台积电(如本文所述)。如前所述,英特尔根本没有谈论晶体管密度这一事实可能会导致一些谨慎。

如上所述,假设英特尔即将推出的所有产品都缩水 2 倍的验证来自前首席执行官 Bob Swan 在 2019 年的评论,以及 Pat Gelsinger 的声明,即未来十年它将遵循摩尔定律。如前所述,台积电落后的一个原因可能是在开发环栅晶体管方面遇到了麻烦。

投资者建议

我目前认为台积电的制程领导地位正在崩溃,比任何人(包括我自己)之前预期的都要严重。

首先,实际测量证实 N5 的密度至少比之前在技术出版物中报道的密度低 20%(~1.25 倍)。其次,由于复合定律,这意味着 N3 的密度也低于之前的预期。这反过来意味着英特尔 3 可能几乎与 N3 相匹敌。第三,虽然英特尔将在 6 个月和 12 个月内分别以 20A 和 18A 跟进英特尔 3,但台积电已将 N2 置于 36 个月的长周期中。此外,台积电的最新披露表明,逻辑晶体管密度将增加不到 30%。

从这个意义上说,英特尔的追赶将类似于台积电最初是如何获得其工艺领导地位的:只需(几乎)遵循摩尔定律,而其他公司则面临着大大减缓它们的问题。

这最终意味着台积电将以难以置信的速度和惊人的数量失去其密度领导地位。英特尔将在 2024 年初凭借英特尔 3 几乎赶上 N3,在明年以 20A/18A 实现近 2 倍的领先地位,然后到 2026 年底将其领先地位进一步提升至 3 倍。

评论